Perusahaan pembuat FPGA seperti Xilinx, Altera pada umumnya menyediakan beberapa cara untuk proses download program ke dalam FPGA. Proses download yang dimaksud di sini adalah sebuah proses memindah program yang telah berhasil diuji dan disimulasikan dari komputer ke dalam FPGA untuk kemudian di lihat hasilnya. Bisa dibilang proses ini adalah untuk melihat hasil secara langsung dari program yang telah disimulasikan. Metode download yang mudah dan sering dipakai adalah dengan menghubungkan komputer (PC) dengan FPGA menggunakan kabel. Untuk penghubung ke PC, kabel yang biasa digunakan terhubung dengan port USB atau port paralel pada PC. Kabel jenis ini biasanya diberi istilah kabel JTAG.

Lalu, apa sebenarnya JTAG? JTAG (Joint Test Action Group) adalah aturan standar dari IEEE (1149.1) yang berkembang pada tahun 1980. Aturan ini dibuat dan dikembangkan dengan tujuan menyelesaikan masalah-masalah pada perakitan sirkuit elektronik (PCB).

Pada umumnya sebuah PCB yang rumit dan kompleks terdiri atas beberapa IC. Misalnya IC gerbang logika, IC untuk mikrokontroler, dsb. Sedangkan tiap-tiap IC memiliki karakteristik kaki (pin) yang berbeda-beda. Lalu sekarang timbul masalah yakni bagaimana untuk mengatur koneksi atau hubungan antara satu IC dengan IC yang lain dalam sebuah PCB? Atau bagaimana mengatur koneksi antara sebuah PCB dengan PCB lain? Untuk mengatasi masalah tersebut, dibuatlah aturan JTAG ini.

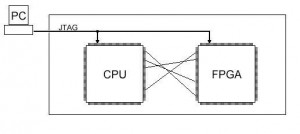

Koneksi PC-CPU-FPGA dengan menggunakan JTAG

JTAG ini berfungsi untuk mengatur koneksi pin-pin di semua IC yang ada. Misalkan, sebuah data hendak dikirimkan ke sebuah board PCB yang di dalamnya terdapat IC FPGA dan IC CPU. JTAG akan memastikan koneksi/jalur yang menghubungkan antara PC, CPU, dan FPGA terlah tersambung dengan baik agar data tersebut sampai pada tujuan yang diinginkan. Untuk menjalankan fungsinya, JTAG terbagi atas 4 sinyal logika. Sinyal ini masing-masing memiliki fungsi tersendiri dan khas serta terpisah satu sama lain. Sinyal-sinyal tersebut yakni:

1. TDI (Test Data Input)

2. TDO (Test Data Output)

3. TMS (Test Mode Select)

4. TCK (Test Clock)

Koneksi JTAG

Dari gambar di atas, terlihat bahwa jalur sinyal TMS dan TCK terhubung secara paralel serta termasuk jenis sinyal input. Sedangkan sinyal TDI merupakan input bagi CPU kemudian outputnya menjadi TDO dan masuk sebagai input ke TDI IC FPGA. Jadi untuk setiap JTAG memiliki 4 pin (3 input dan 1 output). Hingga saat ini, proses pengujian IC (IC boundary test) dilakukan dengan menggunakan JTAG. Lalu, apakah JTAG hanya berfungsi untuk proses pengujian IC? Tentu tidak. Salah satu fungsi yang lain dari JTAG yakni untuk proses konfigurasi pada FPGA. Pengguna FPGA akan mampu mengirimkan data berupa program yang telah dibuatnya ke dalam FPGA dengan bantuan JTAG ini. Demikian sekilas gambaran tentang JTAG.

Mustaghfiri Asror

Mustaghfiri Asror

Posted in:

Posted in:

0 komentar:

Posting Komentar